# A STUDY OF HIGH-SPEED ANALOG-COMPUTER PERFORMANCE (THE ASTRAC I SYSTEM PERFORMANCE)\*

### by Thomas A. BRUBAKER \*\*

Assistant Professor

#### ABSTRACT

Increased interest in high-speed hybrid analog/digital computation has led to the development of the Arizona Statistical Repetitive Analog Computer (ASTRAC I), which employs inexpensive digital logic to control a high-speed repetitive analog computer. The design of the machine has been described elsewhere; this paper reports the results of the error analysis performed on the linear analog computing elements and digital timing circuits. The results are of particular interest for the design of new computing systems of this type.

The results of several statistical experiments are also included to further illustrate the operation and application of the various ASTRAC I computing elements.

Introduction to the ASTRAC I Computer.

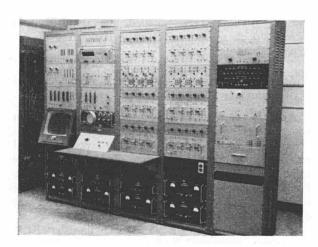

The Arizona Statistical Repetitive Analog Computer (ASTRAC I, fig. 1), described in detail in references [3, 5, 6, 7, 8, 9, 11, 13, 17, 21, 24 and 32], combines

Fig. 1. — The ASTRAC Computer.

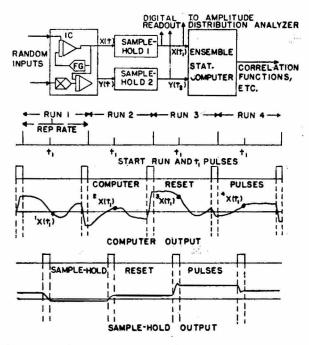

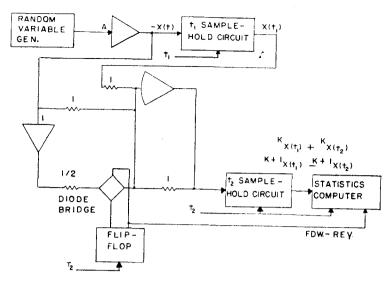

a new fast memory-equipped repetitive/iterative analog computer with digital logic and control. The resulting synthesis of high-speed analog computation with digital automatic programming is of particular interest in connection with Monte-Carlo-type studies of random processes, which serve to illustrate ASTRAC I system operation in figure 2 [4, 41].

Referring to figure 2, an analog-computer simulated control system, communications system, queuing problem, etc., is supplied random inputs, initial conditions, and/or random parameters from noise generators with Gaussian or statistically known random outputs. Reset pulses from a simple digital control unit cause repetitive

simulation of the process under study between 10 and 100 times per second at computing frequencies of 10 to 10,000 radians per second. Accurate sample-hold (analog memory) units read selected process variables at push-button preset times  $t_1$  and  $t_2$  seconds after the start of each computer run. A hybrid analog/digital statistics computer accepts these samples to compute statistical averages over 100 to 9900 computer runs, as determined by a preset run counter in the control unit. In this manner, one can estimate ensemble averages such as mean-square error, correlation functions, and probabilities for very complicated non-stationary as well as stationary random processes.

While the ASTRAC I system is intended mainly for an academic program of graduate instruction and re-

Fig. 2. — A typical repetitive-analog-computer set up together with four sample computer runs.

<sup>\*</sup> Manuscript received September 27, 1963.

<sup>\*\*</sup> The University of Wyoming, College of Engineering

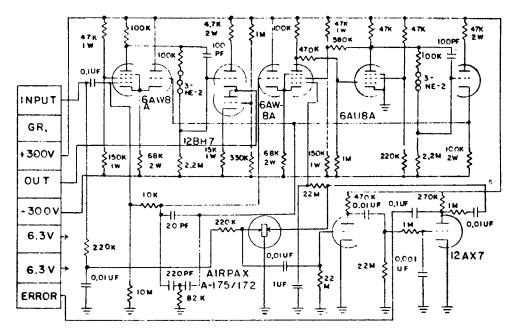

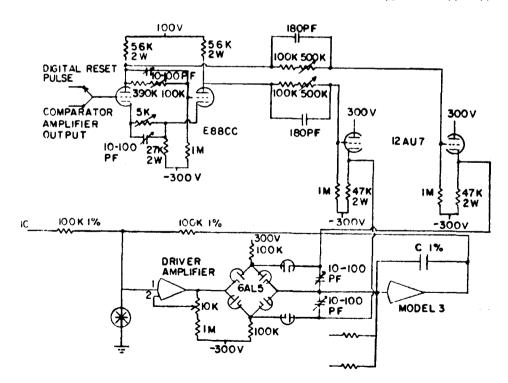

Fig. 3. — Model 3 circuit diagram.

search, some of the new components and design philosophy may be of interest to industrial designers of hybrid analog/digital computing equipment.

### DETAILED ACCURACY STUDIES AND THEIR EFFECT ON COMPUTER-SYSTEM DESIGN

1. Dynamic Characteristics of the University of Arizona Model 3.

Amplifier (fig. 3).

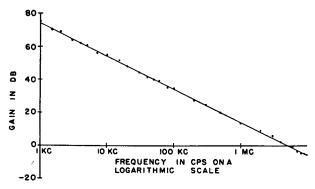

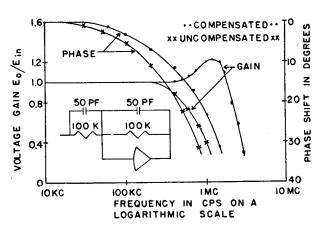

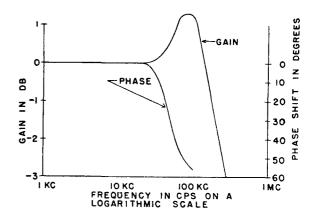

For high-speed repetitive computers, the zero db point of the high-gain d-c operational amplifier must extend well beyond one megacycle in such a way that the amplifier has good stability. Figure 4 shows the open-

Fig. 4. — Model 3 Frequency response.

loop response of the University of Arizona Model 3 amplifier. For stability, the 20 db per decade roll-off extends about 5 mc beyond the zero point, and the measured value of the phase margin is about 30 degrees. Consequently, the amplifier performs well in the usual feedback configurations. In particular, it is short-circuit

stable, and will drive 1000 pf of load capacitance without instability.

The d-c gain of the amplifier is greater than 100 db, and for high-speed computation, the amplifier gain exceeds 70 db at frequencies up to 10,000 radians per second (about 1600 cps).

### Static and Dynamic Characteristics of the Inverter | Summing Amplifiers.

A static test for the summing amplifiers was run with a single, known, d-c input voltage. The output voltage was then measured with a 0.1 percent digital voltmeter and the error was recorded as the absolute value of the desired output minus the actual value. For 1.0 percent computing resistors, the maximum error was 0.7 percent of half-scale and the average error was 0.55 percent of half-scale.

A theoretical equivalent circuit, including the effects of resistor compensation, for summing amplifiers is

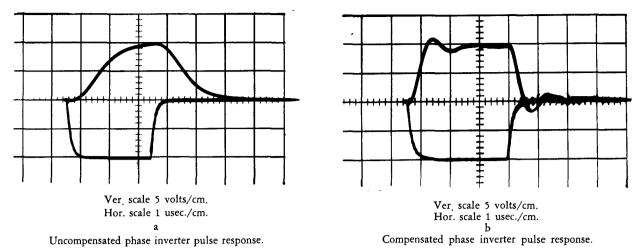

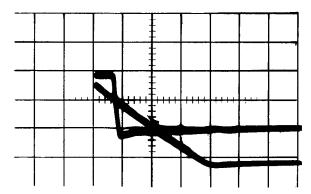

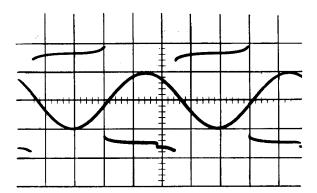

Fig. 5. — Compensated and uncompensated inverter gain of 1 frequency response.

Fig. 6. — Oscilloscope photograph of the compensated and umcompensated inverter pulse response.

discussed in reference [26]. To dramatically illustrate the effect of shunt capacitor compensation of summing amplifier resistors, the compensated and uncompensated gain and phase curve for an inverter are plotted in figure 5. The pulse response for the two cases is shown in figure 6.

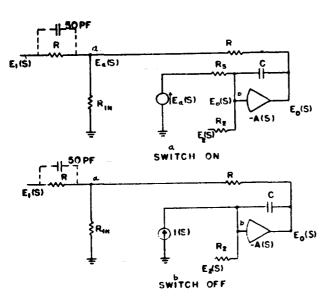

### 3. The Equivalent Circuit Analysis for the Electronically Reset Integrators or Sample-Hold Circuits (fig. 7).

For analysis, the equivalent circuit of an electronically reset integrator is shown in figure 8. For normal operating frequencies, the switch impedance, the driver output impedance, and the driver input impedance, are considered to be resistive.

With the switch ON, the current equation at node (a) can be written in Laplace form as

$$\frac{E_1(s) - E_a(s)}{R} + \frac{E_0(s) - E_a(s)}{R} = \frac{E_a(s)}{R_{in}}.$$

(1)

At node  $\langle b \rangle$ ,

$$\frac{E_{a}(s) - E_{b}(s)}{R_{s}} + \frac{E_{0}(s) - E_{b}(s)}{1/C_{s}} + \frac{E_{2}(s) - E_{b}(s)}{R_{2}} = 0.$$

(2)

Letting

$$E_0(s) = -A(s) E_b(s)$$

(3)

Fig. 7. — ASTRAC 1 electronically reset integrator or sample-hold circuit. For integrators the driver amplifier is a Philbrick K2-XA. For sample-hold circuits the cathode follower resistors are  $33\mathrm{K}\Omega$  the bridge resistors  $33\mathrm{K}\Omega$  and the driver amplifier is a University of Arizona Model 2 with 10 ma output current.

and solving equations (1) and (2) for E<sub>0</sub>(s) gives

$$E_{0}(s) = \frac{-E_{1}(s) - E_{2}(s) R_{s} (R + 2 R_{in}) / R_{2} R_{in}}{1 + \frac{sCR_{s} (R + 2 R_{in})}{R_{in}} + \frac{sCR_{s} (R + 2 R_{in})}{A(s) R_{in}} + \frac{(R_{2} + R_{s}) (R + 2 R_{in})}{A(s) R_{2} R_{in}}}$$

(4)

Equation (4) can now be separated into two parts to study the effective rejection of  $E_2(s)$  and the tracking response to  $E_1(s)$ .

If  $E_1(s)$  is zero, equation (4) can be approximated at low frequencies by

$$E_0(s) \approx -E_2(s) \frac{R_s (R + 2 R_{in})}{R_2 R_{in}}$$

(5)

Furthermore, for  $R_s \ll R_{in}$  and  $R \ll R_2$ , equation (5) can be again approximated to give

$$E_0(s) \approx -E_2(s) \frac{2 R_s}{R_0}. \tag{6}$$

In the time domain,

$$E(t) \approx -E_2(t) \frac{2 R_s}{R_2}. \tag{7}$$

In ASTRAC I,  $R_2$  is 100K $\Omega$  or 500K $\Omega$  and the value of  $R_6$  is found by measuring  $E_0(t)$  for a known  $E_2(t)$

and applying equation (7). For practical purposes, the driver amplifier output impedance is zero which makes  $R_{\rm s}$  equal to the switch impedance, which in general is non-linear. The value of  $R_{\rm s}$  was found to be equal to or less than 300 ohms, which corresponds to a maximum value of 310 ohms taken from a linear approximation to the diode curves. The maximum rejection error is then  $\pm$  0.6 volts for each  $100 \mathrm{K}\Omega$  input and  $\pm$  0.12 volts for each  $500 \mathrm{K}\Omega$  input.

In the steady state, the open-loop amplifier gain can be written

$$A(j_{\omega}) = \frac{A_0}{1 + i \, \delta_{\lambda}(\omega)} \tag{8}$$

where  $A_0$  is the d-c gain and  $\delta_A(\omega)$  is, in general complex, but usually proportional to  $\omega$  over a wide range of frequencies (fig. 4).

For  $E_2(s)$  equal to zero and for a sinusoidal input, substitution of equation (8) into equation (4) gives the steady state gain equation

$$E(j\omega) = -E_{1}(j\omega) \left\{ 1 + \frac{(R_{2} + R_{s})(R + 2R_{in})}{A_{0}R_{2}R_{in}} - \frac{\omega CR(R + 2R_{in})\delta_{A}(\omega)}{A_{0}R_{in}} - \frac{i\omega CR(R + 2R_{in})\delta_{A}(\omega)}{A_{0}R_{in}} - \frac{i\omega CR(R + 2R_{in})\delta_{A}(\omega)}{A_{0}R_{in}} + \frac{i\omega CR(R + 2R_{in})\delta_{A}(\omega)}{i\omega A_{0}R_{2}R_{in}} + \frac{i\omega CR(R + 2R_{in})\delta_{A}(\omega)}{i\omega A_{0}R_{2}R_{in}} \right] \right\}^{-1}.$$

(9)

Fig. 8. — Equivalent circuit for a electronically reset integrator.

The measured frequency response with the 50 pf input compensating capacitor included, is shown in figure 9.

Equations (7) and (9) indicate that for good rejection and frequency response the switch impedance should be low, the driver input impedance high, and the

Fig. 9. — Frequency response of a gain of 1 electronically reset integrator or sample-hold circuit in TRACK.

operational amplifier bandwidth and gain should be as high as possible.

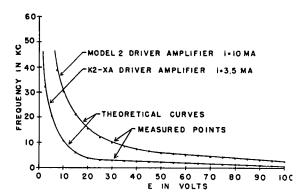

Although the use of either the K2-XA or the Model 2 as the driver amplifier results in the same small-signal frequency response, their current outputs for charging the capacitor are not the same and must be considered when investigating the dynamic characteristics of integrators and sample-hold circuits in RESET or TRACK. For a sinusoidal input

$$E_1(t) = E \sin \omega t \tag{10}$$

the voltage-current relation for a capacitor can be used to find the maximum tracking frequency for a given amplitude E. In equation form

$$f = \frac{i}{2\pi CE} \tag{11}$$

where *i* is the smallest current output of the driver or operational amplifier, E is the amplitude of the input sine-wave, and C is the value of the integrating capacitor. The theoretical and experimental results coincide very well and are shown in figure 10 for  $C = 0.005 \mu f$ .

Fig. 10. — Amplitude-frequency response of electronically reset integrators and sample-hold circuits with current as a parameter.

From this, the sample-hold circuits can be said to track at  $2 \times 10^6$  volts per second and the integrators at  $7 \times 10^5$  volts per second.

With the switch OFF, the equivalent circuit is shown in figure 8 b. Here, the constant current generator corresponds to the switch leakage current and causes the capacitor to charge or discharge at a constant slow rate during COMPUTE or HOLD. For  $C = 0.005 \mu f$ , the circuit will hold within 50 mv for 100 msec. More accurate holding can be obtained at the expense of frequency response by using a larger capacitor.

### 4. Integrator Drift, Offset, and Switching Errors. \*

D-c drift, d-c offsets, switching delays, switching offsets, and switching transients are sources of error in electronically reset integrators, and must be minimized for accurate simulation work.

The d-c drift of the integrators is less than  $\pm$  20 mv after a warm up periode of 15 minutes. D-c offsets are balanced out with a potentiometer and normally are

\* Writers Note. There have been questions as to what integrator drift and offset mean in electrically reset integrators and I wish to clarify this.

The *d-c* offset of an electronically reset integrator is caused by a *d-c* offset in the switch when the switch is ON. This causes a *d-c* offset or initial condition error to appear at the output of the integrator. When the switch turns OFF the integrator then starts to operate from its initial condition which includes the offset error. Now if the integrator uses a chopper stabilized *d-c* amplifier, the major error source in COMPUTE comes from switch leakage current for which the error per unit time is given on page 15. (Note: The offset only causes error in following integrators, and this is the same as an initial condition error.)

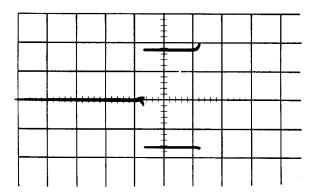

Fig. 11. — Schmitt trigger response to the computer reset pulse. The fast pulse is the Schmitt trigger output.

Ver. scale 20 volts/cm.

Hor. scale 5 usec./cm.

Fig. 12. — Push-pull pulses for the control of the electronic switch. For clarity, the *d-c* levels have been set to show one pulse above the other.

Ver. scale 20 volts/cm. Hor. scale 0.5 msec./cm.

Fig. 13. — Schmitt trigger response to a sine-wave. Ver. scale for the pulses 20 volts/cm. Ver. scale for the sine-wave 0.5 volts/cm. Hor. scale 0.2 msec./cm.

held within ± 50 mv over a two week period with no adjustment.

Figure 11 shows an oscilloscope photograph of the computer reset pulse and one side of the corresponding Schmitt trigger response.

Figure 12 is a photograph of the resulting push-pull pulses, which drive the electronic switch. The Schmitt triggers all switch at about zero volts (fig. 13), and the

switching delay between the various integrators is less than 0.5  $\mu$ sec. Consequently, the effects of integrator switching delay are so small that they are masked by the normal switching transients.

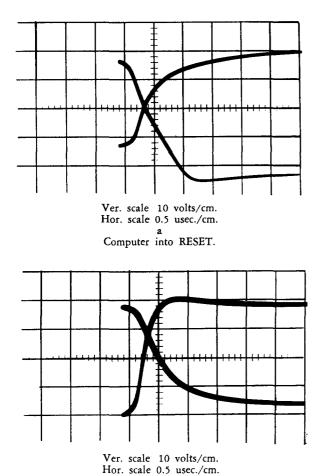

After being adjusted to give zero switching offset at the integrator output, the rise and fall times of the switch control pulses are shown in figure 14. Note

Computer into COMPUTE.

Fig. 14. — Rise and fall times of the switch control pulses.

that the pulses cross zero at exactly the same time going into RESET, which indicates that the electronic switch is turning ON symmetrically. This is not the case going into COMPUTE, and the difference is due to a non-symmetrical turn-off characteristic in the particular switch. In practice, the control pulses for each switch are adjusted separately to give zero switching offset and further adjustment is required about once a month to compensate for component aging.

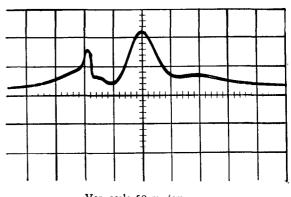

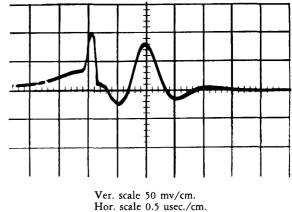

Transients at the integrator output are caused by the switching action; and their amplitude depends on the value of the integrating capacitor. When computing, these transients ride on top of the computer solution and usually contribute a small d-c error after they are damped out. Figure 15 is a photograph of typical integrator switching transients with  $C = 0.01 \,\mu f$ . For values of C up to  $0.001 \,\mu f$ , the transients increase to a maximum value of 200 mv. However, in each case they are damped to less than 50 mv in about  $2 \,\mu sec$ .

Due to a better dynamic response, the transients in the sample-hold circuits have a maximum value of 400 mv and also damp out in about 2  $\mu$ sec.

Ver. scale 50 mv/cm. Hor. scale 0.5 usec./cm.

Computer into RESET.

b Computer into COMPUTE.

Fig. 15. — Switching transients at the output of an electronically reset integrator.

### 5. Integrator Response to a Step Function.

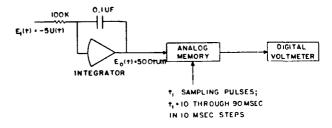

Although integrators do not, strictly speaking, operate in static modes, a quasi-static integrator test consisted of measuring the integrator response to a 5 volt step function (rate test). The computer setup is shown in figure 16. The integrator output was sampled every 10 msec, and the digital voltmeter was used to read the sample value. For readout accuracy, the memory pair used for readout was calibrated within 50 mv.

Fig. 16. — Computer setup for integrator rate test.

The test was run over all possible  $100 \mathrm{K}\Omega$  integrator inputs and the results are tabulated in table 1.

### 6. Dynamic Errors in Linear Computing Loops.

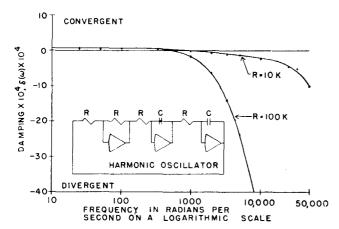

Dynamic errors in computer setups for the solution of linear, constant coefficient, differential equations, can be described in terms of perturbations of the characteristic roots and generation of extraneous roots. The modes of operation due to the extraneous roots are usually strongly damped, and the characteristic root perturbations alone, can be used as a measure of dynamic errors in linear computing elements. These perturbations, which are caused mainly by phase shift, show up especially well in sinusoidal solutions. (This does not necessarily mean that the percentage errors are higher in sinusoidal solutions; it only means they are easier to see). The well known harmonic oscillator computer setup (fig. 17), for the solution of the differential equation

$$\frac{d^2x}{dt^2} = -\omega^2 x \tag{12}$$

demonstrates such a situation and serves as a sensitive test for the phase shift in linear computing elements (circle test). Writing the characteristic equation of equation (12) in Laplace form gives

$$s^2 + \omega^2 = 0 \tag{13}$$

and permits the classical representation of the characteristic roots as

$$s_{1,2} = \pm j_{\omega}. \tag{14}$$

For X(0) = B and  $\dot{X}(0) = 0$ , the solution of equation (12) is

$$x(t) = B \cos \omega t. \tag{15}$$

## Table 1 INTEGRATOR RATE TEST

Note: The integrator rate test was run by patching — 5 volts d-c into all 36 of the 100K integrator inputs.

| Sampling<br>time in<br>msec. | Theoretical value in volts | Average<br>value in<br>volts | Average<br>error in<br>volts | Maximum<br>error in<br>volts |

|------------------------------|----------------------------|------------------------------|------------------------------|------------------------------|

| 10.0                         | 5.0                        | 5.1                          | -0.1                         | 0.2                          |

| 20.0                         | 10.0                       | 10.0                         | 0.0                          | 0.3                          |

| 30.0                         | 15.0                       | 15.2                         | 0.2                          | 0.2                          |

| 40.0                         | 20.0                       | 20.1                         | 0.1                          | 0.3                          |

| 50.0                         | 25.0                       | 25.0                         | 0.0                          | 0.4                          |

| 60.0                         | 30.0                       | 29.9                         | 0.1                          | 0.4                          |

| 70.0                         | 35.0                       | 34.9                         | 0.1                          | 0.4                          |

| 80.0                         | 40.0                       | 39.8                         | 0.2                          | 0.6                          |

| 90.0                         | 45.0                       | 44.7                         | 0.3                          | 0.7                          |

The actual computer solution has a characteristic equation of the form

$$s^2 + 2 \delta \omega_n s + \omega_n^2 = 0$$

(16)

with roots

$$s_{1,2} = -\delta \omega_n \pm j\omega \tag{17}$$

where

$$\omega_n^2 (1 - \delta^2) = \omega^2 \tag{18}$$

and  $\omega$  is the natural frequency with no damping. Normally, the magnitudes of the real parts of the roots are much smaller than the magnitudes of the imaginary parts, and  $\omega$  is approximately equal to  $\omega_n$ . If this is the case, the characteristic roots can be written

$$s_{1,2} = -\delta \omega \pm j \omega. \tag{19}$$

In analog computers,  $\delta$  is a function of  $\omega$  and for x(0) = B and  $\underline{x}(0) = 0$ , the actual computer solution is approximately

$$x(t) = B e^{-\omega \delta(\omega)t} \cos \omega t. \qquad (20)$$

Fig. 17. — Harmonic oscillator computer setup.

It is interesting to note that, since  $\delta(\omega)$  is caused by phase shift, it can be either positive or negative; in most computers, the sign may change, possibly more than once, over the frequency range of the computer [35].

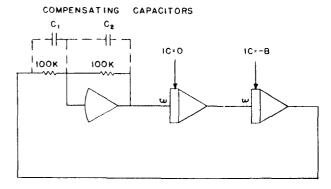

Figure 18 is a plot of  $\delta(\omega)$  for ASTRAC I simulations of equation (12). For demonstration purposes, the simulation was run using various compensating capacitors connected in parallel with the inverter resistors. This dramatically illustrates the effect of small phase shifts in computing loops. The equation was also set up using a potentiometer in the loop, but no appreciable change occurred. This indicates that the

Fig. 18. — Damping characteristics of the ASTRAC I harmonic oscillator computer setup.

low-resistance potentiometers used in ASTRAC I do not contribute objectionable phase shift.

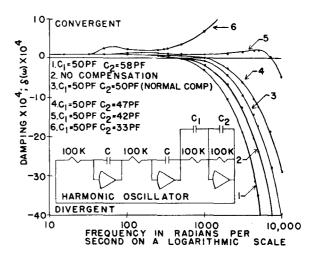

Experimental results and equivalent circuit studies of linear computing elements, indicate that dynamic errors are smaller if short leads and particularly, low computing impedances are used in conjunction with wideband, high-gain, operational amplifiers [26]. To test this theory, the solution for the harmonic oscillator equation was simulated on ASTRAC I using 10K carbon resistors and very short wiring. The results are shown in figure 19, and vindicate the theory quite

Fig. 19 — Damping characteristics for a low impedance and high impedance ASTRAC I harmonic oscillator computer setup.

well. The important thing to consider is that the use of low impedances permits the utilization of the complete amplifier band-width and amplifier limitations will be the determining factor in high frequency dynamic errors. Note that this also requires a high-current amplifier.

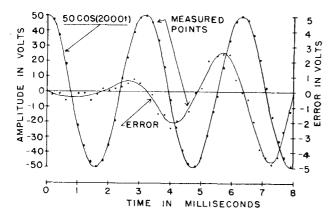

When a timed sampling readout is used to plot computer solutions, small frequency errors can cause large amplitude errors, as shown in figure 20. Here,

Fig. 20. — Amplitude error of timed samples due to a small frequency perturbation.

the experimental points indicate that the solution frequency is lower than the theoretical value and, although the experimental waveform is quite sinusoidal, the amplitude errors are large as the solution goes through

zero. To illustrate this further, consider the harmonic oscillator solution

$$x(t) = 100 \sin \omega t \tag{21}$$

where

$$\frac{1}{\sqrt{R_1 C_1 R_2 C_2}} \tag{22}$$

For a one-percent error in  $R_1$ , the resulting amplitude-time error is 3.14 volts per cycle as the solution goes through zero. Note that this error is the same for all frequencies.

In most simulations, this effect is not too important and can be treated as a small frequency perturbation. However, if amplitude errors are to be investigated from sample points, the effect of frequency error must be considered.

### 7. Effects of Timing Errors in the Digital Control Unit.

Errors in the digital control unit are caused by variations in the timing intervals due to the following causes:

- 1. Deviation of the oscillator frequency from 10 kc.

- 2. Delays due to « ripple-through-time » in the digital counters and digital circuits.

The crystal oscillator has a measured frequency of 9992.2  $\pm$  .1 cps, which results in a mean time interval of 0.10000785 msec. This alters each computing interval, but its greatest effect is on  $t_1$  and  $t_2$  timing. For example, if the computer solution

$$x(t) = 100 \sin(5000 t + \theta) \tag{23}$$

were to be sampled by presetting  $t_1$  at 50 msec, the true sampling time would be 50.03925 msec, which gives a timing error of 0.03925 msec or 0.0785 percent. If the maximum rate of change of x(t) is considered as constant over this time interval, the sample value would be in error by 19.625 volts or almost 20 percent of half-scale.

The delays of the various resetting pulses are tabulated in table 2. Table 3 shows the delays of the  $t_1$  and  $t_2$  sampling pulses with the 100 cps repetition rate used as a reference.

Although the oscillator frequency error is uniform, the sampling pulse time delays are not. To investigate this further, suppose the crystal oscillator frequency is exact and the only error is due to «ripple-through-delay». If the waveform of equation (23) passes through zero at a theoretical time of 6 msec, and is sampled then by the  $t_1$  sample-hold circuit, the delay error of 8.5  $\mu$ sec would cause the sample value to be in error by 4.25 volts.

Originally, the crystal oscillator was intentionally detuned for statistical studies; but in the near future, the addition of a commercial, temperature stabilized, crystal oscillator will permit the clock frequency to be set accurately at 10 kc. For most well designed experiments, even the fast repetition rate permits solutions of low enough frequency, so that the sampling delay errors are not too important. However, faster computers of this type will require transistorized digital control units which are designed using modern logic schemes. The delays in such control units will be in the order of tenths of microseconds.

Table 2 COMPUTER RESET PULSE DELAY

| Repetition rate in runs/second | Delay<br>in μsec. |  |

|--------------------------------|-------------------|--|

| 100                            | 5.0               |  |

| 50                             | 7.0               |  |

| 25                             | 7.5               |  |

| 10                             | 8.5               |  |

|                                |                   |  |

Table 3 SAMPLING PULSE DELAY

Note: All delays were measured with respect to the 100 cps repetition rate.

| Samplin time in msec. | Delay<br>in μsec. | Sampling time in msec. | Delay<br>in μsec. |

|-----------------------|-------------------|------------------------|-------------------|

| 0.1                   | 1.0               | 6.0                    | 8.5               |

| 0.2                   | 2.5               | 7.0                    | 3.0               |

| 0.3                   | 0.5               | 8.0                    | 5.5               |

| 0.4                   | 3.0               | 9.0                    | 3.0               |

| 0.5                   | 0.5               | 10.0                   | 4.0               |

| 0.6                   | 5.5               | 20.0                   | 8.5               |

| 0.7                   | 0.5               | 30.0                   | 6.0               |

| 0.8                   | 3.0               | 40.0                   | 9.5               |

| 0.9                   | 0.5               | 50.0                   | 6.0               |

| 1.0                   | 3.0               | 60.0                   | 13.0              |

| 2.0                   | 5.0               | 70.0                   | 6.0               |

| 3.0                   | 3.0               | 80.0                   | 9.0               |

| 4.0                   | 6.0               | 90.0                   | 6.0               |

| 5.0                   | 3.0               |                        |                   |

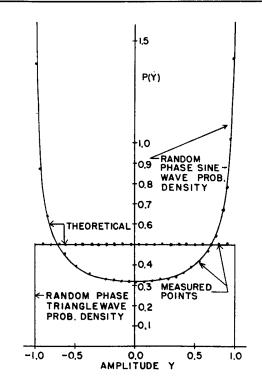

Fig. 21. — Probability densities for a random phase sinewave and a random phase triangle-wave.

The above discussion vindicates the choice of a digital control system for ASTRAC I. It is questionable to generate accurate timing pulses using a comparator and a linear analog voltage. The analog signals simply are not accurate enough.

# EXPERIMENTAL RESULTS: RANDOM-PROCESS STUDIES

### 1. Measurement of Cumulative Probability Distributions and Probability Densities.

Figure 21 shows normalized probability density functions for a random phase sine-wave and a random phase triangle-wave. Each waveform had an amplitude of 20 volts peak-to-peak.

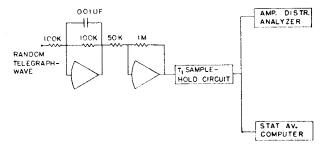

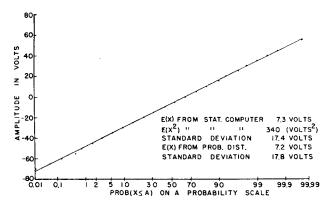

The computer setup for generation of a Gaussian random variable, x(t), and the measurement of the cumulative distribution function, E[x(t)], and  $E[x(t)^2]$

Fig. 22. — Computer setup for the measurement of the cumulative distribution function of gaussian noise.

Fig. 23. — Cumulative distribution for gaussian noise generated by filtering a random telegraph wave.

is shown in figure 22. Figure 23 is a plot of the distribution function on probability paper along with tabulated values of the standard deviation and mean value. The curve indicates that the waveform is Gaussian to a good approximation.

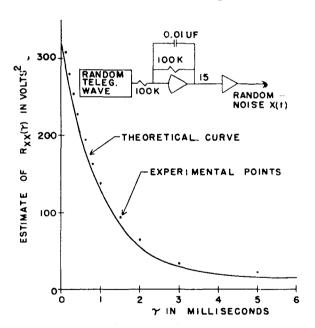

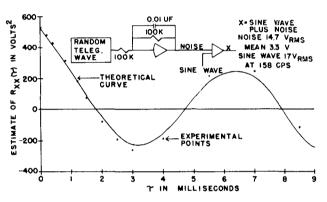

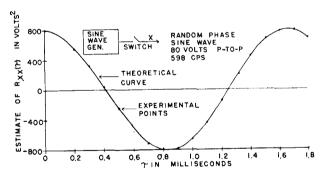

### 2. Autocorrelation Function Measurements.

Conant has measured autocorrelation functions for Gaussian noise, Gaussian noise plus a sine-wave, and a random phase sine-wave [11]. The Gaussian noise was obtained by filtering a random telegraph wave. The computer setup used for the experiment is shown

Fig. 24. — Computer setup for the measurement of autocorrelation functions.

in figure 24 and the results are plotted in figures 25, 26 and 27. An important result is that the Gaussian noise is essentially uncorrelated for samples separated by more than 5 msec in time.

### 3. Other Projects.

In addition to the problems discussed above, ASTRAC I has worked on the following:

Fig. 25. — Autocorrelation function for gaussian noise generated by filtrering a random telegraph wave.

- 1. Measurement of the mean-square of speech samples (Engineering Research Laboratory project).

- 2. Injection of artificial errors into alternate repetitive analog computer solutions (parameter perturbation; EE 272/3 term paper).

- Simulation of steel-on-steel impact with analog memory techniques (Analog/Hybrid Computer Laboratory project).

Fig. 26. — Autocorrelation function for a sine-wave plus noise.

Fig. 27. — Autocorrelation function of a random phase sinewave.

- One-parameter automatic optimization by a new parameter perturbation method (solution of a boundary-value problem; Analog/Hybrid Computer Laboratory project).

- 5. Demonstration of a projectile trajectory with randomly disturbed initial conditions (Analog/Hybrid Computer Laboratory project).

- 6. Study of different optimization criteria for nonlinear control systems with random-noise inputs [36].

#### Conclusions.

- The ASTRAC I computer has proven to be a relatively accurate high-speed repetitive analog computer, which is well suited for studies of deterministic processes, stationary and non-stationary random processes, and parameter optimization. In addition, this new machine has already proved useful as a teaching aid illustrating the idea of ensemble statistics.

- 2. It appears feasible to construct all solid state repetitive analog computers to operate at a repetition rate of 1000 solutions per second, and at computing frequencies up to 50,000 radians per second. Figure 19 clearly indicates that this will require low computing impedances and wideband amplifiers with high current.

### Acknowledgments.

The ASTRAC I project was supported by a considerable amount of M. S. thesis work and graduate student term papers under the writer's nominal supervision. Appreciation is due to H. Koerner, R. Eckes, B. Conant, M. Morgan, H. Handler, R. Streets, J. Manilis, B. Barker, M. McMahan, J. Bailey, F. Shaver, and B. Mitchell, all graduate students at the University of Arizona, for their contributions; only this perfect team effort has made it possible to complete a relatively large system, such as ASTRAC I, as a graduate student dissertation. Credit is also due to a number of undergraduate students who performed much of the actual construction of the ASTRAC I modules.

The author is particularly grateful to his dissertation advisor, Dr. G.A. Korn, for his guidance and inspiration during the course of the research.

Special appreciation is also extended to Dr. P.E. Russell, Head of the Electrical Engineering Department, and Dr. T.L. Martin, Dean of the Engineering College, for their support of the project.

### **BIBLIOGRAPHY**

- [1] ANDREWS, J.M., «Mathematical Applications of the Dynamic Storage Analog Computer,» Proc. WJCC, 1960.

- [2] BAILEY, J.C., and F.H. SHAVER, «An Experimental Chi-Square Probability Density Function,» EE 335 term paper, University of Arizona, May, 1960.

- [3] BARKER, B., and M. McMAHAN, « Digital Voltmeter Employes Voltage-to-Time Converter, » Electronics, May 5, 1961.

- [4] BERGER, E.L., and R.M. TAYLOR, «Optimization of Radar in its Environment by GEESE Technique, » Proc. WJCC, 1961.

- [5] BRUBAKER, T.A., and G.A. KORN, «Accurate Amplitude Distribution Analyzer Combines Analog and Digital Logic, » Review of Scientific Instruments, March, 1961.

- [6] BRUBAKER, T.A., and H.R. ECKES, « A Digital Unit for a Repetitive Analog Computer, » *Proc. WJCC*, 1961.

- [7] BRUBAKER, T.A., « A Precision Analog Memory has Extended Frequency Response, » *Electronics*, September 8, 1961.

- [8] BRUBAKER, T.A., «ASTRAC I Operations Manual,» ACL Memorandum, University of Arizona, 1963.

- [9] BRUBAKER, T.A., « ASTRAC I Maintenance Manual, » ACL Memorandum, University of Arizona, 1963.

- [10] BRUNNER, W., « An Iteration Procedure for Parametric Model Building and Boundary-Values Problems, » Proc. WJCC, 1961.

- [11] CONANT, B.K., « A Hybrid Analog-Digital Statistics Computer, » ACL Memorandum No. 45, University of Arizona, 1962.

- [12] « Dystac Applications, » (Eastern Simulation Council Presentations, December 1960), published by Computer Systems, Inc., Monmouth Junction, N.J., 1960.

- [13] ECKES, H.R., «A Digital Expansion System for ASTRAC I, » M.S. Thesis, University of Arizona, 1963.

- [14] ETERMAN, I.I., Analog Computers, translated from the Russian by G. Segar, Pergamon Press, N.Y., 1960.

- [15] GILLILAND, M.C., «Iterative Differential Analyzer Function and Control, » Instruments and Control Systems, April 1, 1961.

- [16] FIFER, S., Analog Computation: Theory, Techniques and Applications, McGraw-Hill, N.Y., 1961.

- [17] HANDLER, H., and H.R. ECKES, « A Pseudo Random Noise Generator, » EE 335 term paper, University of Arizona, 1963.

- [18] HUSKEY, H.D., and G.A. KORN, Computer Handbook, McGraw-Hill, N.Y., 1961.

- [19] JACKSON, A.S., Analog Computation, McGraw-Hill, N.Y., 1960.

- [20] KARPLUS, W.J., and W.W. SOROKA, Analog Methods: Computation and Simulation, 2nd Ed., McGraw-Hill, N.Y., 1960.

- [21] KOERNER, H., « How to Extend Operational Amplifier Response, » *Electronics*, November 11, 1960.

- [22] KOERNER, H., and G.A. KORN, «Function Generation with Operational Amplifiers, » *Electronics*, November 6, 1959.

- [23] KORN G.A., «Repetitive Analog Computers at the University of Arizona, » Instruments and Control Systems, September, 1960.

- [24] KORN, G.A., «New High-Speed Analog and Analog-Digital Computing Techniques: The ASTRAC System,» 3rd AICA Conference, Opatija, Yugoslavia, September, 1961.

- [25] KORN, G.A., «Performance of Operational Amplifiers with Electronic Mode Switching, » Trans. IRE/PGEC, June, 1963.

- [26] KORN, G.A., and T.M. KORN, Electronic Analog and Hybrid Computers, McGraw-Hill, to be in print, 1964.

- [27] MACNEE, A.B., «Some Limitations on the Accuracy of Electronic Differential Analyzers, » Proc. IRE, March, 1952.

- [28] MACNEE, A.B., « An Electronic Differential Analyzet, » Proc. IRE, November, 1949.

- [29] McFADDEN, J.A., «The Axis-Crossing Intervals of Random Functions, » Trans. IRE/PGIT, December, 1956.

- [30] McFADDEN, J.A., "The Axis-Crossing Intervals of Random Functions II," Trans. IRE/PGIT, March, 1958.

- [31] McFADDEN, J.A., « The Axis Crossings of a Stationary Gaussian Markov Process, » *Trans. IRE/PGIT*, July, 1961.

- [32] MANELIS, J., « A Scintillation-Detector Noise Generator for Fast Analog Computation, » *Electronics*, September 8, 1961

- [33] MEISSINGER, H.E., « Parameter Influence Coefficients and Weighing, Functions Applied to Perturbation Analysis of Dynamic Systems, » 31d AICA Conference, September, 1961.

- [34] MORGAN, M., «Experimental Determination of the Probability Density Function of a RC-Low-Pass Filter with a Poisson Wave Input, » EE 335 term paper, University of Arizona, 1961.

- [35] SINGLE, C.H., and E.M. BILLINGHURST, «Optimization of Analog Computer Linear System Dynamic Characteristics, » Proc. WJCC, 1961.

- [36] STREETS, R.B., « A Study of Different Optimization Criteria for Non-linear Control Systems with a Random Noise Input, » ACL Memorandum No. 52, University of Arizona, 1962.

- [37] TOMOVIC, R., « New Applications of an Electronic Function Generator, » Trans. IRE/PGEC, March, 1958.

- [38] TOMOVIC, R. and W.J. KARPLUS, High-Speed Repetitive Analog Computers, Wiley, N.Y., 1962.

- [39] WADEL, L.B., «An Electronic Differential Analyzer as a Difference Analyzer,» JACM, July 1954.

- [40] WADEL, L.B., «Automatic Iteration on an Electronic Analog Computer,» Proc. WESCON, 1954.

- [41] VAN DER VELDE, W.E., «Make Statistical Studies on Analog Simulations,» Control Engineering, June, 1960.

- [42] DOW, P.C., «An Analysis of Certain Errors in Electronic Differential Analyzers, I-Bandwidth Limitations, II-Capacitor Dielectric Absorption, » Trans. IRE-PGEC, December, 1957.

- [43] MARSOCCI, V.A., «An Error Analysis of Electronic Analog Computers, » Trans. IRE-PGEC, December, 1956.

- [44] MIURA, T. and M. NAGATA, «Theoretical Considerations of Computing Errors of a Slow Type Electronic Analog Computer, «Trans. IRE-PGEC, December, 1958.